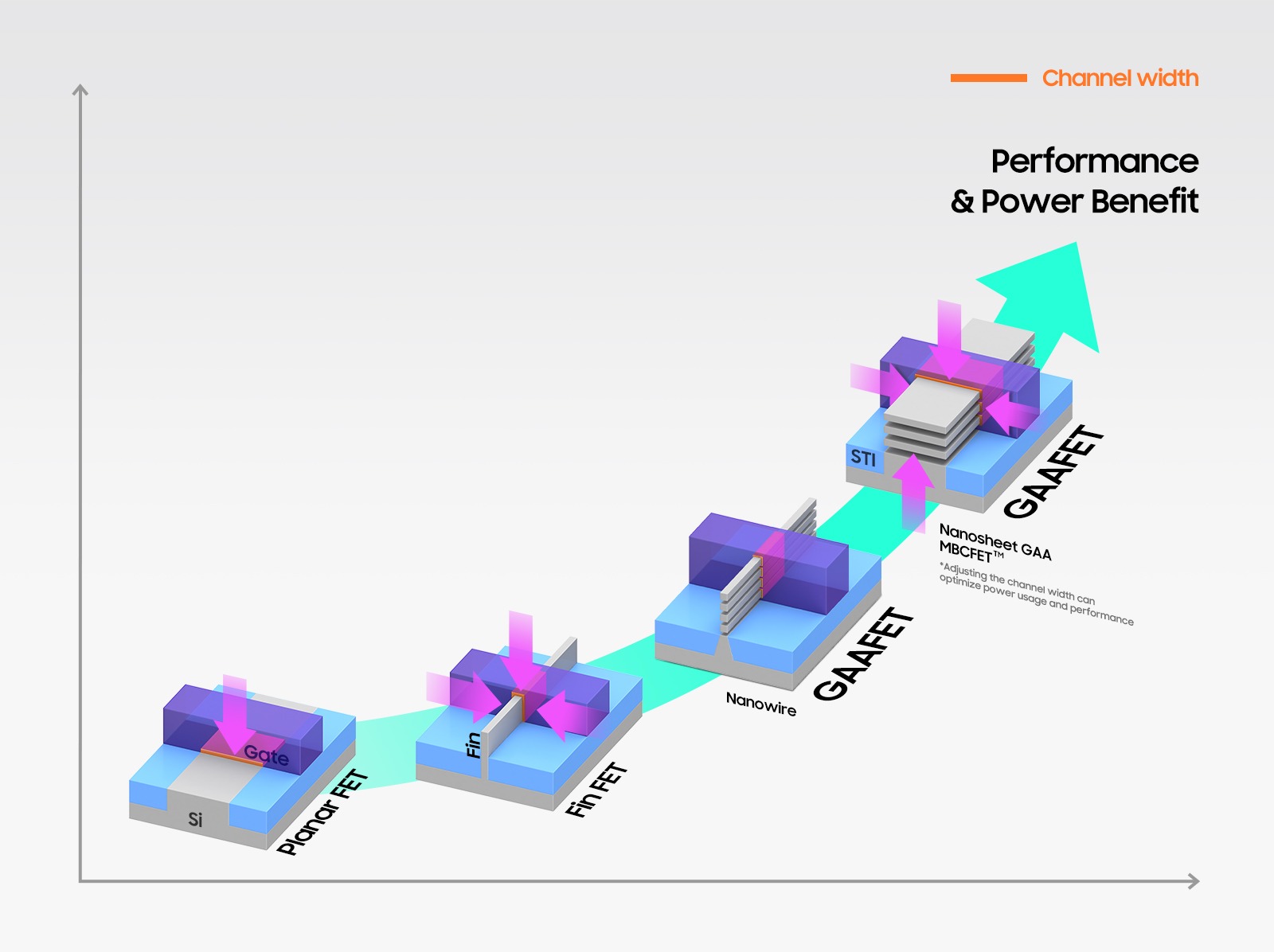

Die Halbleitersparte Samsung Foundry gab bekannt, dass sie in ihrem Werk in Hwasong mit der Produktion von 3-nm-Chips begonnen hat. Im Gegensatz zur Vorgängergeneration, die die FinFet-Technologie nutzte, verwendet der koreanische Riese nun die GAA-Transistorarchitektur (Gate-All-Around), was die Energieeffizienz deutlich steigert.

3-nm-Chips mit MBCFET-GAA-Architektur (Multi-Bridge-Channel) werden unter anderem durch eine Reduzierung der Versorgungsspannung eine höhere Energieeffizienz erzielen. Samsung setzt Nanoplättchentransistoren auch in Halbleiterchips für leistungsstarke Smartphone-Chipsätze ein.

Im Vergleich zur Nanodrahttechnologie ermöglichen Nanoplatten mit breiteren Kanälen eine höhere Leistung und bessere Effizienz. Durch die Anpassung der Breite der Nanoplättchen können Samsung-Kunden Leistung und Stromverbrauch an ihre Bedürfnisse anpassen.

Das könnte Sie interessieren

Im Vergleich zu 5-nm-Chips haben die neuen laut Samsung eine um 23 % höhere Leistung, einen um 45 % geringeren Energieverbrauch und eine um 16 % kleinere Fläche. Ihre 2. Generation soll dann eine um 30 % bessere Leistung, einen um 50 % höheren Wirkungsgrad und eine um 35 % kleinere Fläche bieten.

„Samsung wächst schnell, da wir weiterhin eine führende Rolle bei der Anwendung von Technologien der nächsten Generation in der Fertigung unter Beweis stellen. Unser Ziel ist es, diese Führungsposition mit dem ersten 3-nm-Prozess mit der MBCFETTM-Architektur fortzusetzen. Wir werden weiterhin aktiv Innovationen bei wettbewerbsfähigen Technologieentwicklungen vorantreiben und Prozesse schaffen, die dazu beitragen, das Erreichen der Technologiereife zu beschleunigen.“ sagte Siyoung Choi, Leiter des Halbleitergeschäfts von Samsung.